Dataflow Management (Architecture) with Model-Based Design for SAR Signal Processing on FPGA

DOI:

https://doi.org/10.37934/ard.135.1.169182Keywords:

GB-SAR, SLC image, nested loop, Simulink, MBD, HDL coder, FPGAAbstract

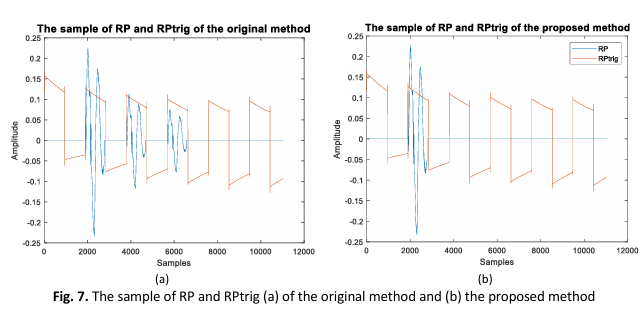

The signal processing in ground-based synthetic aperture radar (GB-SAR) has two main processes. One is the pre-processing data to prepare the data; the other is an algorithm to establish the single-look complex (SLC) image. Normally, the pre-processing data process wastes time recording huge signals for processing and a nested loop inside the process. In this paper, we propose a dataflow management approach for the pre-processing data process to overcome the wasted time on recording data. Against the nested loop, we proposed model-based design (MBD) techniques that support the Hardware Description Language (HDL) coder in Simulink. The proposed method performs well without a nested loop and can be implemented on the Xilinx Zynq Z-7020 Field Programmable Gate Array (FPGA) board, which is a low-cost FPGA. From the result, our proposed method has a high average percentage error in some stages, but the output from the final stage gives a very low average percentage error. The data after our proposed method can give the SLC image, which has the same significance as the SLC image from the original method. Our proposed implementation can perform on the FPGA as well. Therefore, the proposed method using dataflow management with MBD gives data with a low average percentage error and the SLC image similar to the original method.

Downloads