Design of Advanced Encryption System (AES) Algorithm Using ASIC Implementation for Internet of Things (IoT) Devices

DOI:

https://doi.org/10.37934/ard.123.1.131145Keywords:

AES-128, IoT, S-Box, CMOS technologyAbstract

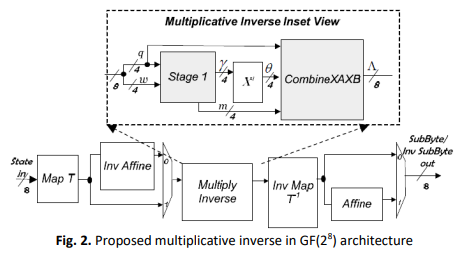

This paper presents an AES-128 configuration designed specifically for IoT devices, utilizing 90nm CMOS technology. The architecture, developed in Verilog HDL and executed through Synopsys tools, incorporates a modified S-Box aimed at enhancing performance, area efficiency, and throughput. The motivation stems from the increasing security requirements of IoT applications, highlighting the need for robust data protection for resource-constrained devices. Versatile for IoT applications, this design handles standard input data block sizes of 128 bits. It stands out as a purpose-built solution for securing digital communications in the IoT, overcoming unique challenges such as limited resources and fluctuating communication environments. The modified S-Box The altered S-Box bolsters security, aids in space optimization, and enhances efficiency compared to prevailing solutions. By using techniques to carefully modify replacement boxes, these designs deliver optimized performance from both a safety and space utilization perspective. Extensive validation work, including Synopsys tool testing and simulation, ensures the reliability of the proposed AES-128 design. It achieves a throughput of 14.54Mbps at a clock frequency of 100MHz while maintaining a compact footprint of 0.4324mm2 to meet the constraints of IoT devices. The practical implications of this design lie in the balance between performance and resource utilization, making it suitable for real-world IoT implementations. The utilization of a 128-bit key length augments security, rendering the proposed AES-128 an ideal choice for safeguarding data across diverse IoT applications.

Downloads