Performance Evaluation of Cryptographic Algorithms on Reconfigurable Hardware: MD5 based on Timing and Area Implementation

Keywords:

FPGA, Frequency Maximum, Grey, HDL, MD5Abstract

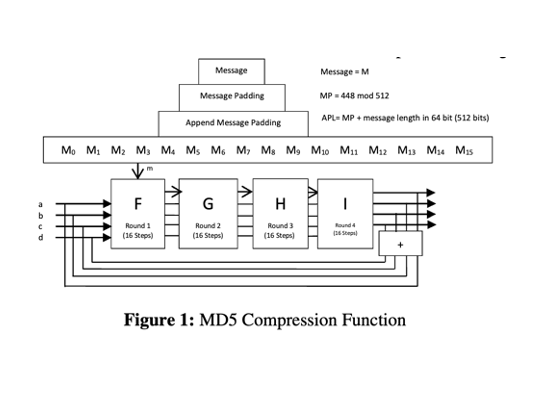

Cryptographic algorithm has become one of the most important aspects in hardware implementation of embedded security system design. Message Digest (MD) is one of the cryptographic algorithms that can be used in any security design application. Nowadays, designing the high speed,

low power, and small area implementation of cryptographic algorithms on reconfigurable hardware is

one of the critical subjects for hardware application. The purpose of this paper had been to analyse the

structure of MD5 hash function for high performance implementation in order to obtain small area

implementation, as well as to increase the speed of the design on FPGA. In this paper, the frequency

maximum for MD5 design with both grey and binary signal encoding is discussed. The results retrieved

from the analysis showed that the differing results were caused by the switching bit of the signal input.

Besides, the frequency maximum of MD5 that employed binary signal encoding provided the highest

frequency maximum with smaller area implementation. By using grey signal encoding, the frequency

maximum was almost similar to the MD5 binary signal encoding, but it suffered larger area

implementation. On top of that, this research focused on timing and area implementation of the design,

where TimeQuest timing analyser was applied to optimize the output of the design.

Downloads