Low Power 7 nm FinFET based 6T-SRAM Design

Keywords:

7nm Bulk FinFET, 6T-SRAM, BSIM-CMG, RSNM, WLWM, standby powerAbstract

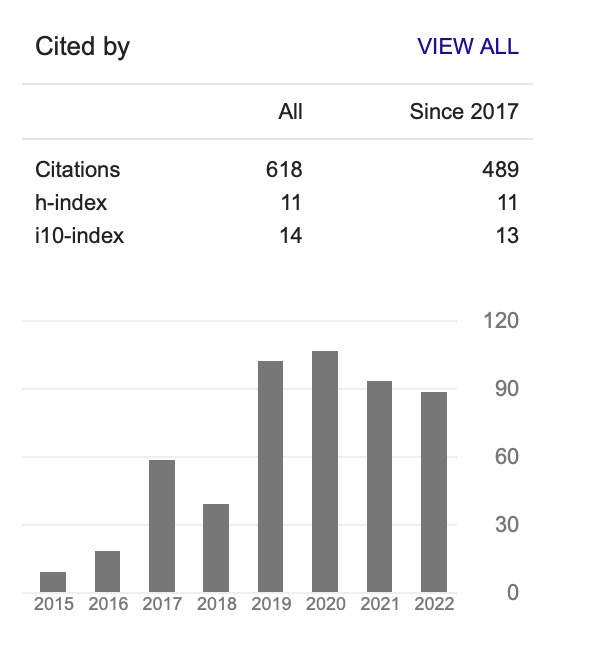

FinFET based SRAM design makes the SRAM more appealing in the low power applications. This paper presents a 7 nm FinFET device characterization utilizing the compact model BSIM-CMG. In addition, the paper provides simulations for different stability parameters, access time, and standby power of two 6T-SRAM cells designs consisting of different fin count. The standby power for both cells are 149 and 198 pW/µm with better read stability for the later design while the access time is constant for both cells (30 ps). The read/write operation of the two SRAM cells is stable with reducing the power supply to 0.5 V.